以太网:

以太网(Ethernet)是一种计算机局域网技术。

以太网通常分为两个主要层次:物理层和数据链路层。

物理层:

- 物理层规定了以太网的基本物理属性,如数据编码、时标、电频等。(简单来说就是提供接口)

- 物理层位于OSI参考模型的最底层,它直接面向实际承担数据传输的物理媒体(即通信通道)。物理层的传输单位为比特(bit),即一个二进制位(“0”或“1”)。实际的比特传输必须依赖于传输设备和物理媒体,但是,物理层不是指具体的物理设备,也不是指信号传输的物理媒体,而是指在物理媒体之上,为上一层(数据链路层)提供一个传输原始比特流的物理连接。

数据链路层:

- 数据链路层是OSI参考模型中的第二层,介于物理层和网络层之间。数据链路层在物理层提供的服务的基础上向网络层提供服务,其最基本的服务是将源设备网络层转发过来的数据可靠地传输到相邻节点的目的设备网络层。

- 由于以太网的物理层和数据链路层是相关的,针对物理层的不同工作模式,需要提供特定的数据链路层来访问。这给设计和应用带来了一些不便。为此,一些组织和厂家提出把数据链路层再进行分层,分为媒体接入控制子层(MAC)和逻辑链路控制子层(LLC)。这样不同的物理层对应不同的MAC子层,LLC子层则可以完全独立。

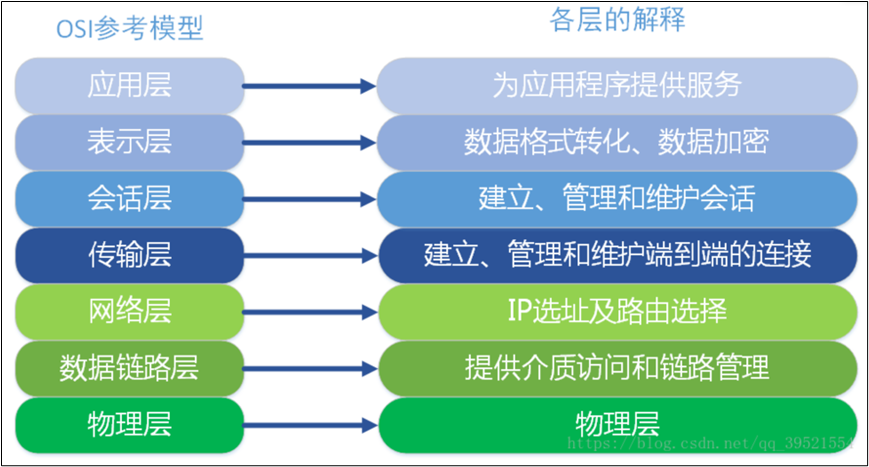

OSI 7层模型:

OSI(Open System Interconnect),即开放式系统互连,一般都叫OSI参考模型,是ISO(国际标准化组织)组织在1985年研究的网络互连模型。

OSI定义了网络互连的七层框架(物理层、数据链路层、网络层、传输层、会话层、表示层、应用层),即ISO开放互连系统参考模型。

W5500芯片特点:

- W5500 是一款全硬件 TCP/IP 嵌入式以太网控制器,为嵌入式系统提供了更加简易的互联网连接方 案。W5500 集成了 TCP/IP 协议栈,10/100M 以太网数据链路层(MAC) 及物理层(PHY),使得 用户使用单芯片就能够在他们的应用中拓展网络连接。

- W5500支持标准的以太网通信,可以实现可靠的数据传输,适用于各种网络应用。

- 支持硬件TCP/IP协议:TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE。

- 内置 8 个独立硬件 Socket,可同时处理 8 路网络连接,适合多任务并发场景。

- 集成10/100M 以太网数据链路层(MAC)及物理层(PHY)。

- 具备掉电模式和网络唤醒功能,采用高速 SPI 接口(模式0,3)。

- W5500内置了用于数据存储和缓存的内存,有助于提高数据传输效率(32K字节)。

- W5500采用了低功耗设计,有助于在电源有限的嵌入式系统中实现节能。

- 支持自动协商(10/100-Based 全双工/半双工)。

- 不支持 IP 分片。

- 3.3V 工作电压,I/O 信号口 5V 耐压。

- LED 状态显示(全双工/半双工,网络连接,网络速度,活动状态)。

SocKet含义解释:(套接字)

- Socket 就是 W5500 内部的“独立小房间”,每个房间可以同时干不同的网络任务,互不干扰。

- 包含:

- 协议类型(TCP/UDP)

- 本地IP和端口

- 目标IP和端口(仅需在主动连接时指定)

- 开发时配置:

- “开房间”:初始化 Socket(选模式、设端口)。

- “派任务”:发送/接收数据。

- “查状态”:看房间忙不忙。

W5500芯片适用领域:

家庭网络设备: 机顶盒、个人录像机、数码媒体适配器

串行转以太网: 门禁控制、LED 显示屏、无线 AP 继电器等

并行转以太网: POS/微型打印机、复印机

USB 转以太网: 存储设备、网络打印机

GPIO 转以太网: 家庭网络传感器

安全系统: 数字录像机、网络摄像机、信息亭

工厂和楼宇自动化控制系统

医疗监测设备

嵌入式服务器

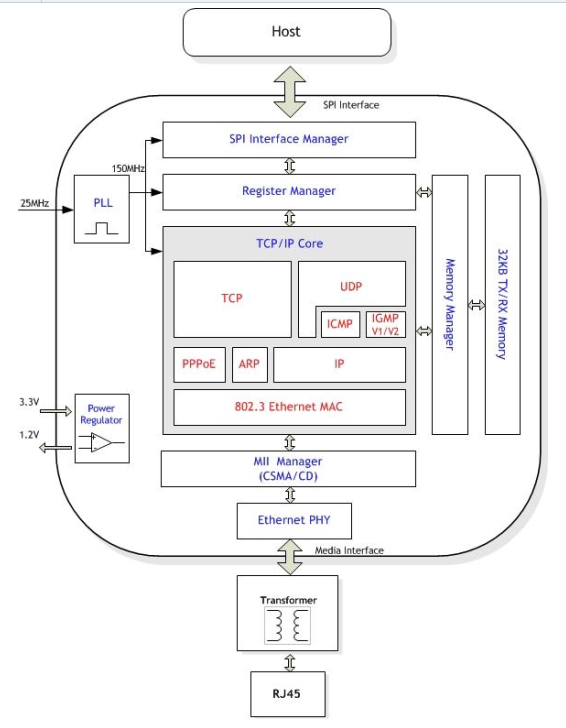

W5500原理框架图:

- 芯片外围有时钟接口、电源接口,SPI通信接口,以及以太网数据收发接口。芯片内部主要分为SPI接口管理,芯片寄存器管理,收发缓存管理,传输层的各种通信协议,网络层的IP协议,链路层的MAC,连接链路层和物理层的MII接口,以及最后的物理层。

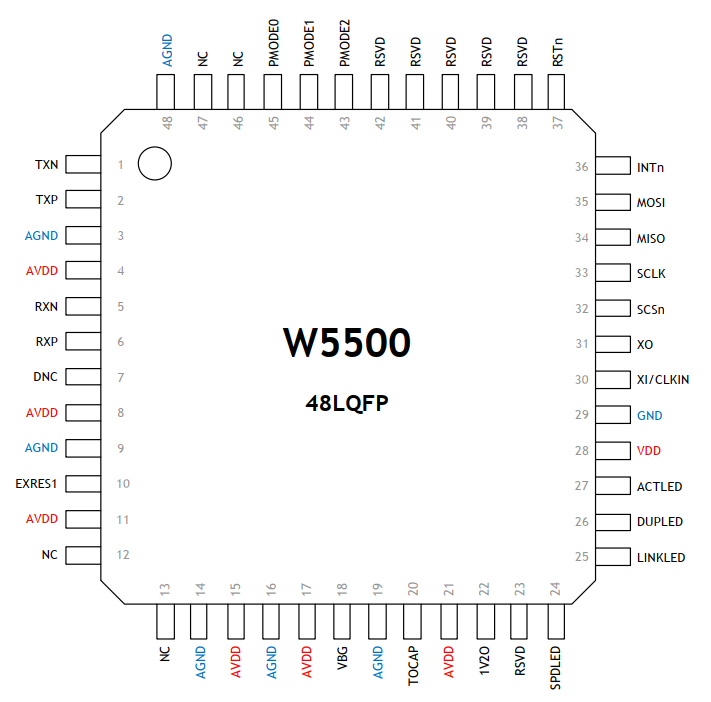

W5500电路引脚图:

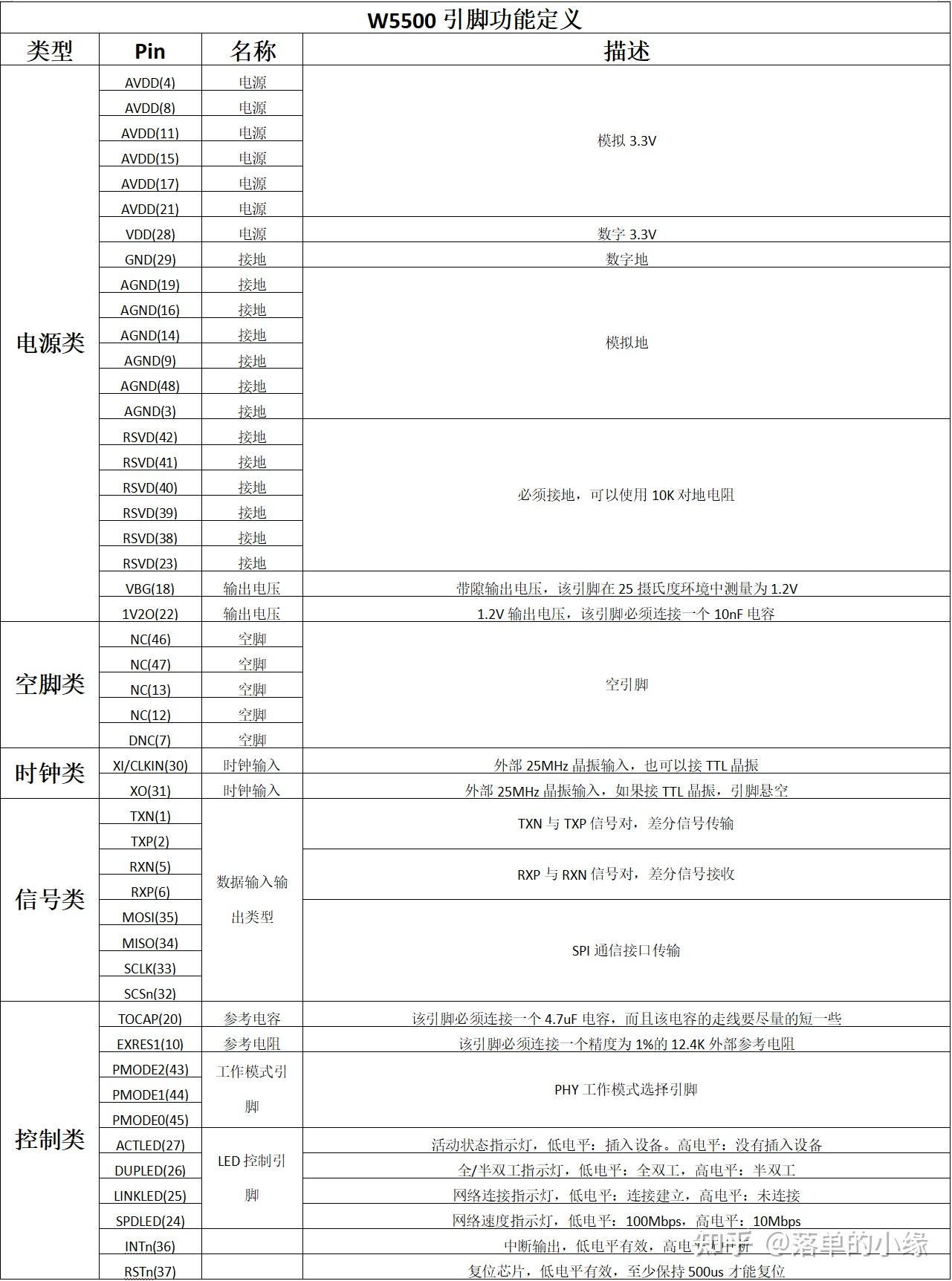

W5500引脚介绍:

STM32主控芯片与W5500交互:

SPI连接

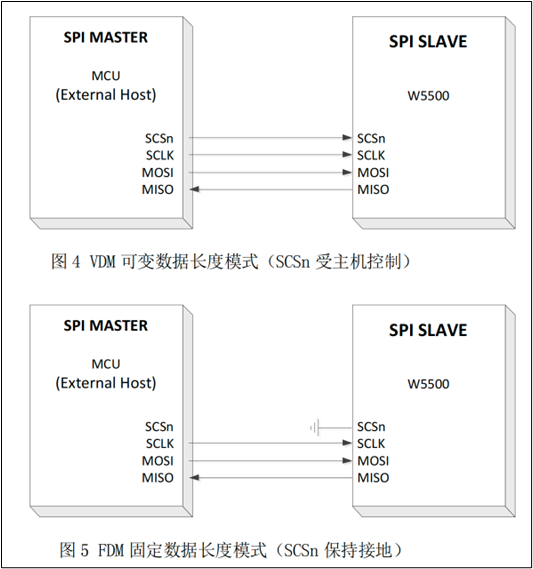

W5500提供了SPI(串行外部接口)作为外设主机接口,有SCSn、SCLK、MOSI、MISO 共4路信号,且作为SPI从机工作。

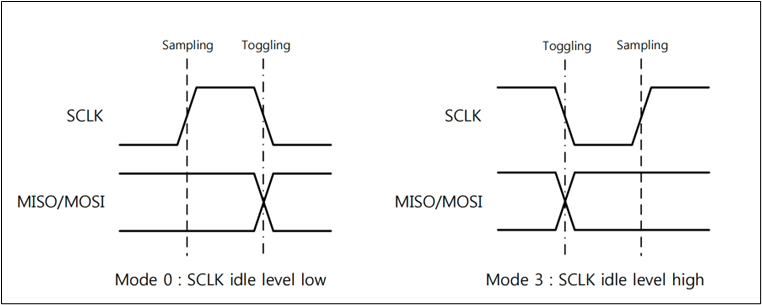

在W5500中只支持工作模式0和3,在这两种模式下数据总是在SCLK信号的上升沿被锁存,在SCLK信号的下降沿被输出。

MOSI和MISO信号无论是接收或发送,均遵从最高标志位(MSB)到最低标志位(LSB)的传输序列。

固定数据长度模式和可变数据长度模式:

- 如果SPI工作模式设置为可变数据长度模式(VDM),SPI的SCSn信号需要由外部主机通过SPI帧控制。

- 在可变数据长度模式下,SCSn控制SPI帧的开始和停止:SCSn信号拉低(高电平到低电平),即代表W5500的SPI帧开始(地址段);SCSn信号拉高(低电平到高电平),即代表W5500的 SPI帧结束(数据段的随机N字节数据结尾)。

W5500的内部存储器:

- 1个普通寄存器block:这里配置了W5500的一些基本信息,如网络配置(IP、MAC地址、Socket中断配置等)。

- 8个Socket寄存器block:这里配置了每个Socket对应的信息,如Socket的模式、命令、状态、中断信息等。

- 8个Socket对应的接收缓冲寄存器block(共16k):初始时每个Socket分配为2k的缓存,用户可以自己重新通过修改相应的配置寄存器进行修改,但是要保证分配给8个Socket的缓冲大小之和不能超过16k,否则会报错。

- 8个Socket对应的发送缓冲寄存器block(共16k)。