DMA概述:

直接存储器存取(direct memory access,DMA)用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输,无须CPU干预,数据可以通过DMA快速地移动,这就节省了CPU的资源来做其他操作。

STM32F103共有

2个DMA控制器,12个通道(DMA1有7个通道,DMA2有5个通道),每个通道专门用来管理来自于一个或多个外设对存储器访问的请求,还有1个仲裁器来协调各个DMA请求的优先权。DMA控制器和Cortex™-M3核心共享系统数据总线,执行直接存储器数据传输,当CPU和DMA同时访问相同的目标(RAM内存或外设)时,DMA请求会暂停,CPU访问系统总线达若干个周期,总线仲裁器执行循环调度,以保证CPU至少可以得到一半的系统总线(存储器或外设)带宽。

- 存在两种情况:

- 情况一:CPU让给DMA先使用数据总线,等DMA结束后,CPU再用

- 情况二:CPU先让给DMA先使用,在中间的时候CPU可以使用,然后再转给DMA使用,比如在使用串口发送和接收数据的时候,在等数据发送过来的这一段时间,就可以把数据总线交给CPU使用,从而也就提高了效率,这种方式称为周期挪用或周期窃取

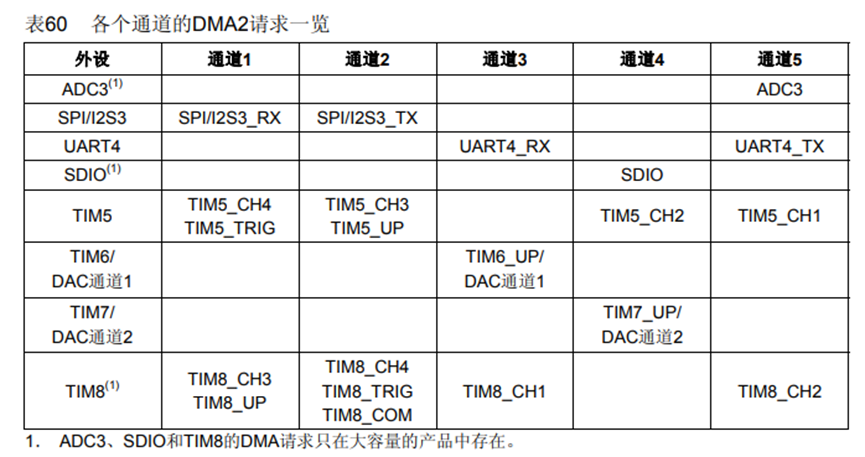

注意:DMA2只存在于大容量产品和互联型产品中。

DMA请求:

如果外设要想通过DMA来传输数据,必须先给DMA控制器发送DMA请求,DMA控制器收到请求信号之后,控制器会给外设一个应答信号,当外设得到控制器的应答信号后,外设会立即释放它的请求。

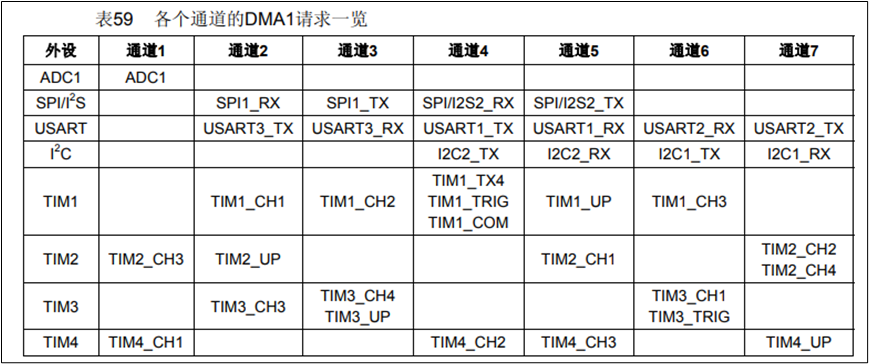

DMA有DMA1和DMA2两个控制器,DMA1有

7个通道,DMA2有5个通道,不同DMA控制器的通道对应着不同的外设请求,这决定了我们在软件编程上该怎么设置。

DMA通道:

- DMA具有

12个独立可编程的通道,其中 DMA1有7个通道,DMA2有5个通道,每个通道对应不同的外设的DMA请求。虽然每个通道可以接收多个外设的请求,但是同一时间只能接收一个,不能同时接收多个。

DMA仲裁器:

- 当发生多个DMA通道请求时,就意味着有先后响应处理的顺序问题,这个就由仲裁器管理。仲裁器管理DMA通道请求分为两个阶段。

- 第一阶段:属于软件阶段,可以在DMA_CCRx寄存器中设置,有

4个等级:非常高、高、中和低,四个优先级。 - 第二阶段:属于硬件阶段,如果两个或以上的DMA通道请求设置的优先级一样,则他们优先级取决于通道编号,编号越低优先权越高,比如通道

1高于通道2。 - 在大容量产品和互联型产品中,DMA1控制器拥有高于DMA2控制器的优先级。

传输方向:

- 存储器到外设,外设到存储器,存储器到存储器。这里的存储器指的是ROM和RAM。

- 注意:DMA没有办法把数据从RAM传输到ROM(flash)。

配置:

- 时钟使能(AHBENR)

- 设置存储器方向(CCR)

- 设置外设和存储器宽度(CCR)

- 设置外设和存储器地址自增(CCR)

- 传输中断使能(CCR)

- 配置源地址和目的地地址(CPAR、CMAR)

- 数据传输长度(CNDTR)

- 通道传输使能(CCR)